# PAPER Adiabatic Circuits Simulation and Energy Dissipation Comparison at different load capacitance

Nazrul ANUAR<sup>†a)</sup>,

**SUMMARY** The current status of research and development in the field of adiabatic electronic devices for the production of information is reviewed. An adiabatic logic is a technique to design low power digital VLSI. In this presentation, several computer simulations using LTSpice have been carried out on the circuits in [1] - [2] and the total energy dissipation at different load capacitance are compared. *key words:* adiabatic logic

### **Presentation content**

- 2008/09/26 : Circuit Simulation and Energy dissipation at different C

- 2008/10/03 : Circuit Simulation and Energy dissipation at different C (continue)

2008/10/10 : Circuit Simulation with new diagrams

## 1. Introduction

- 1.1 Adiabatic Logic Circuit Group

- 1.1.1 Asymptotically Adiabatic Logic

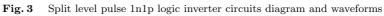

In [1], asymptotically adiabatic logic comprised of circuits in which dissipation results solely from finite rate of change of driving voltage and can be decreased to any desired level. In [1], it is represented by 2n2p-2n logic, 1n1p logic that is using the split-level driving pulses and split-level charge-recovery logic. All the examples are the inverter circuits.

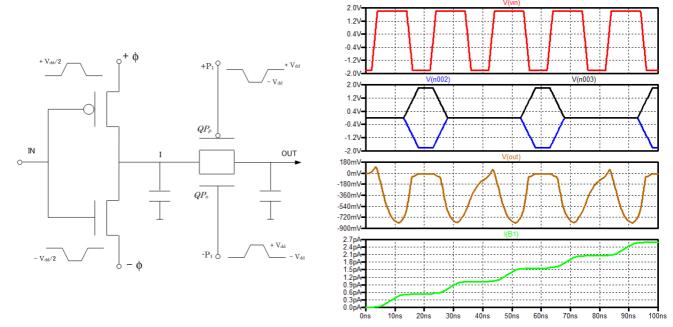

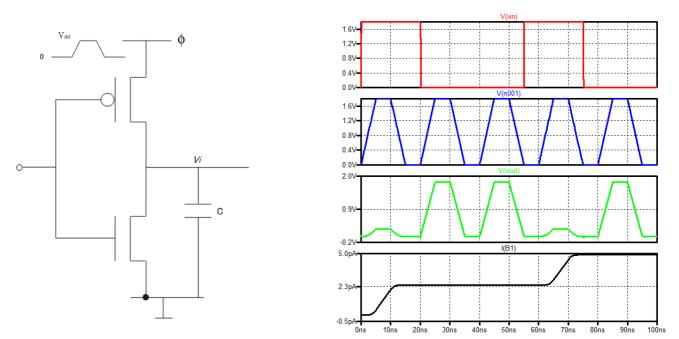

1.1.2 Quasi-Adiabatic Logic

In [1], quasi-adiabatic logic comprised of circuits which dissipation can be reduced appreciably by lowering the rate of change of driving voltage. It is divided into another 2 groups, which is the static approach and the dynamic approach. The static is represented by 1n-1p quasi-adiabatic logic and 2n-2n2p quasi-adiabatic logic. While the dynamic approach is represented by Hotclock nMOS (HCnMOS) logic, recovered-energy logic (REL), Adiabatic Dynamic Logic (ADL) and Efficient charge-recovery logic (ECRL).

#### 2. Simulation and Results

#### 2.1 Conditions

Computer simulations using LTSpice are carried out for all the inverter circuits in [1]. Circuits are connected to the pulse driving voltage and input signal according to the diagrams. Depending on the circuits, the input pulse T (time for 1 cycle) supplied ranging from 20 ns to 55 ns. Length and width of the nMOS and pMOS gates used in this simulation are L=0.18  $\mu$ m, W=0.6  $\mu$ m. The most suitable load capacitor value for each circuits is examined according to the output voltage waveforms. Circuits diagrams and simulation results in the form of waveforms are represented by Fig. 2 – Fig. 13

2.2 Circuits comparison

Table 1 lists the features of all logics in the review for comparison

2.3 Energy dissipation at different load capacitance

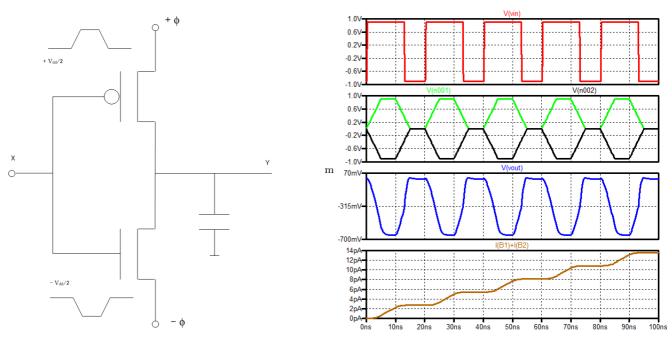

The simulation result on the energy dissipation at different load capacitance is shown in Fig. 14.

## 3. Conclusion

- Analysis of the adiabatic circuits using LTSpice shown that the energy dissipation can be calculated and therefore is convinience for futher analysis and design. In this simulation result, HCnMOS shows the lowest energy dissipation as an inverter

- ADL, ADCL and REL in MOSFETs circuits are still not operating very well in this simulation. Further corrections need to be carried out.

- Load Capacitance which use as the data holder need to be design precisely considering the time constant that effect the output and also the amount of information to be stored

### References

<sup>&</sup>lt;sup>†</sup>The author is with the Department of Electrical and Electronic Engineering, Faculty of Engineering, Gifu University, Gifu-shi, 501-1193 Japan

a) E-mail: n3814101@edu.gifu-u.ac.jp

V.I Starosel'skii "Adiabatic Logic Circuits: A Review," Russian Microelectronics, 2002, Vol.31, No. 1, pp.37-58

- [2] Y. Takahashi, Y. Fukuta, T. Sekine, and M. Yokoyama, "2PADCL : Two Phase drive Adiabatic Dynamic CMOS Logic," *Proc. IEEE APCCAS*, Dec 2006, pp. 1486-1489

- $\mathbf{2}$

Fig. 1 Conventional CMOS logic inverter circuits diagram and waveforms

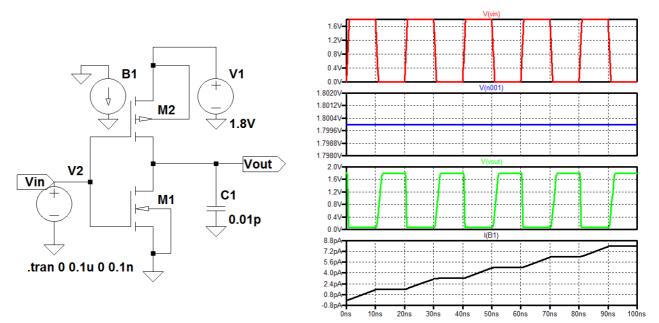

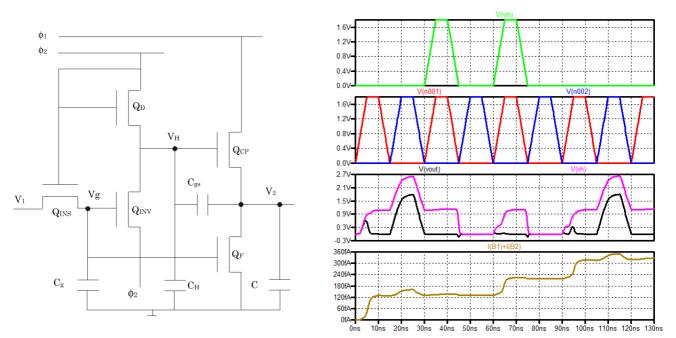

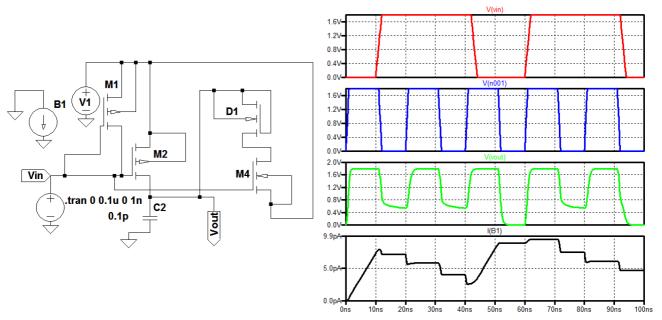

Fig. 2 2n2p-2n adiabatic logic inverter circuits diagram and waveforms

| Table 1 | Comparison | of Power | Dissipation |

|---------|------------|----------|-------------|

|---------|------------|----------|-------------|

| Adiabatic Logic Circuits          | Energy Dissipation (pJ/cycle) | Number of Gates | Driving Pulse |

|-----------------------------------|-------------------------------|-----------------|---------------|

| HCnMOS                            | 0.085                         | 5               | 2             |

| 1n-1p Split level charge recovery | 0.53                          | 4               | 1             |

| ECRL                              | 1.28                          | 4               | 1             |

| Conventional CMOS                 | 1.5948                        | 2               | 1             |

| 1n-1p quasi                       | 2.45                          | 2               | 1             |

| 1n-1p Split level pulse           | 2.71                          | 2               | 2             |

| 2n2p-2n                           | 5.72                          | 6               | 1             |

| 2PADCL                            | 9.2739                        | 4               | 2             |

| 2n-2n2p quasi                     | 11.31                         | 6               | 1             |

| ADL                               | 12.78                         | 4               | 4             |

| REL in MOSFETs                    | 679                           | 4               | 1             |

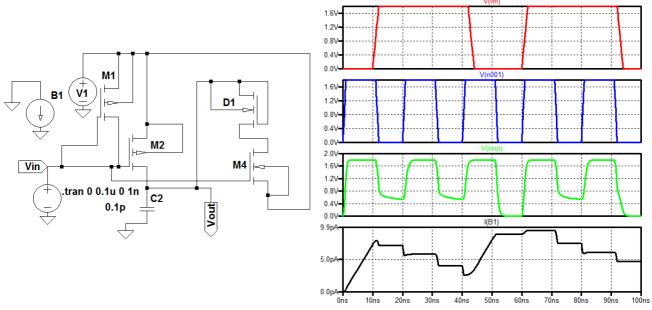

Fig. 4 Split level charge-recovery logic inverter circuits diagram and waveforms

Fig. 5 1n-1p quasi-adiabatic logic inverter circuits diagram and waveforms

Fig. 6 2n-2n2p quasi-adiabatic logic inverter circuits diagram and waveforms

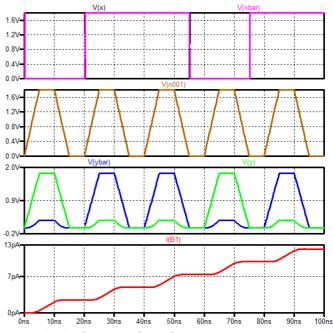

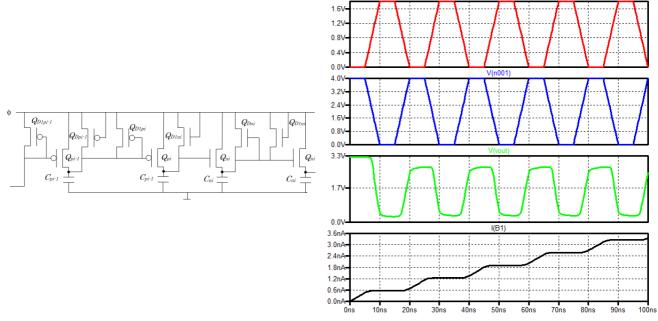

Fig. 7 Hot-clock nMOS logic inverter circuits diagram and waveforms

$\label{eq:Fig.8} {\bf Fig.8} \quad {\rm Recovered-energy \ logic \ (REL) \ in \ MOSFETs \ inverter \ circuits \ diagram \ and \ waveforms$

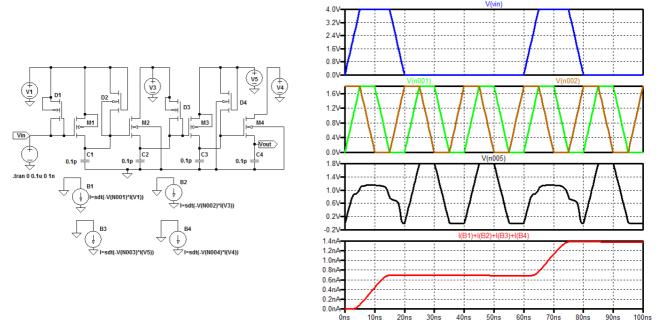

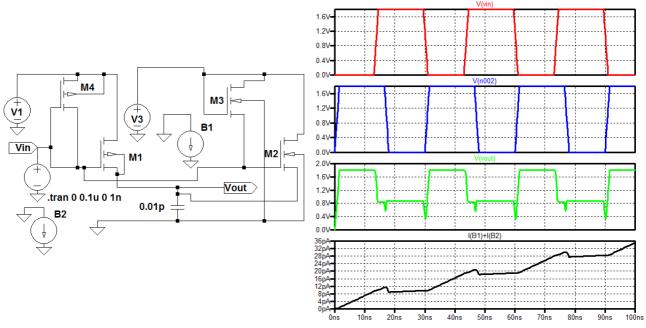

Fig. 9 Adiabatic Dynamic logic (ADL) inverter circuits diagram and waveforms

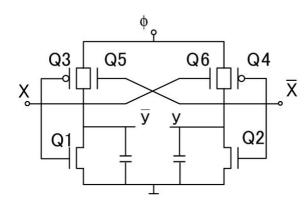

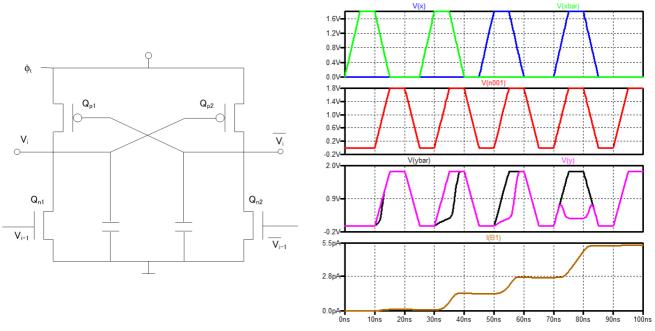

Fig. 10 Efficient charge-recovery logic (ECRL) circuits diagram and waveforms

Fig. 11 Conventional Adiabatic Dynamic CMOS logic (ADCL) circuits diagram and waveforms

Fig. 12 Modified Adiabatic Dynamic CMOS logic (ADCL) circuits diagram and waveforms

Fig. 13  $\,$  Two-phase drive adiabatic dynamic CMOS logic (2PADCL) circuits diagram and waveforms

Fig. 14 Energy dissipation comparison in adiabatic circuits at different load capacitance value