# **Ejectorless Method for Die Attach Pick Up for Cracking Improvement on Thin High-Aspect Ratio Die**

https://doi.org/10.3991/ijoe.v16i08.14727

Ahmad R. A. Rahman <sup>(⊠)</sup>, Nazrul Anuar Nayan National University of Malaysia, Bangi, Malaysia p94324@siswa.ukm.edu.my

Abstract—The demand for producing small, thin, and light electronic devices is increasing. As a result, the design and assembly of electronic packaging technology have been developed. To meet the ever-increasing technology requirements, the critical process in the semiconductor packaging include wafer back grinding, sawing, and die attach. Given that the die thickness is lower than the previous ones, the risk of die cracking failures, which can lead to device malfunction, becomes high. In the die attach process, the ejector pin has an effect during the pick and place processes. Such impact may result in micro dented mark or micro crack underneath the die, which becomes the weakened point throughout the entire process. In this study, an ejectorless system for the die pick and place during the die attach process has been designed and evaluated. The methodology of using ejector pin is replaced by heated static pillar inside cavity for die platform before being picked up. Vacuum is used to stabilize the die, and heat is applied to soften the sawing tape and weaken the adhesion of the die to the sawing tape. Results show that the critical issues of die crack for thin high aspect ratio die are resolved by using the proposed method for the die pick during the die attach process. In conclusion, the semiconductor packaging advances the pick-up technology solution for the challenging material, which is needed for the current miniaturization market trend and demand.

Keywords—Die attach, miniaturization, integrated circuit, packaging process.

#### 1 Introduction

Die attach is a critical integrated circuit (IC) packaging process. However, low die thickness can result in reduced drain-source on resistance, RDS (on), which is the silicon resistance between the top metal and paddle. Thus, improved heat dissipation, minimal stacked up package thickness, and lightweight have been demanded. This threedimensional (3D) technology represents the next wave of packaging innovation and will observe a sharp growth in the future [13]. There are often many hot walls or pipelines at industrial plants even when there is insufficient light or vibration for energy harvesting [18]. With the continuous improvement of technology, the cost of sensor nodes is decreasing and the function is stronger [19]. The trends raise great challenges to existing electronic packaging technology, primarily the die pick up process. This

growth was attributed to the automated manufacturing line employing technology digitization in the industry through the implementation of computer approach and robotic automation [20]. Handling thin dies requires extra attention to ensure the reliability and quality of semiconductor products [6] [10]. In fact, the situation is worsening in recent years because the dies have been thinning increasingly [11]. During the back-grinding process, finished wafer thickness varies on the basis of dry polishing parameters used, and such variations in finished thickness significantly affect the die strength, especially for 75  $\mu$ m wafer [12]. As the thinning of IC chip occurs, the chip cracking between the adhesive tape and ultrathin IC chip increases because of the low strength of the chip in die pick up process [4].

The size of semiconductor dies normally ranges between 0.5 mm and 6.0 mm. The high aspect ratio is defined when a large difference of the die width and length is observed, in other words, rectangular dies with big difference in those two dimensions. This kind of die shape causes challenges to the die attach process because of the uneven stresses of the thin die, which result in die warpage. Furthermore, the stress induced by the thermal mismatch of different materials may affect the assembly processes, which include die mounting, wire bonding, molding, and package singulation [14]. During the die attach process, dies are transferred from sawing tape to the die paddle of a lead frame or substrate. Typically, die pick up uses ejector pin and rubber tip. The ejector pin pushes the die from the bottom. Then, collet picks the die up assisted by the vacuum and then places it on the paddle of the lead frame or substrate. All surfaces and structures of the die need to be well protected during the die pick up process because their presence significantly increases the adhesion and contact angle between the dies and dicing tape [10]. However, the aforementioned methodology does not work for thin dies, which are dies with a thickness of 75 µm or lower. The movements of the ejector pin cause high impact at the bottom of the die, thereby weakening the contact point and causing hairline cracks. This type of minimal cracks will increase into full crack during die attach process. It will further high risks during other subsequent processes in semiconductor packaging assembly, such as wire bonding, molding, lead trimming, lead forming, and reliability during application.

For a die with low thickness (50 to 75  $\mu$ m) and high aspect ratio (i.e., die length is five times more than the width), die warpage due to imbalance stress is identified. Furthermore, the current ejection system highly affects the back of the die, and die hairline cracking occurs during the die attach or subsequent processes. However, the hairline crack is not observable during the die attach processing with monitoring system. It is normally detected during an electrical test. The failure test units will be decapsulated for failure analysis. After decapsulation, further visual inspection will be conducted to determine the root cause of the die crack failure. In this case, the standard die attach process may be unsuitable when using an ejector needle [16].

In typical die attach process, the movement of the die pick up consists of pushing forces from the bottom and pick up force from the top. The pick process is actually composed of two separate actions, namely, peeling the foil from the chip and picking the chip from above with a vacuum tool [9]. During the die pick up process, the change in vacuum force alters the shape of the die, especially during the vacuum release process [1]. Suitable pick up tip or collet is used to ensure that the die is flattened during the

pick and place process. The pick-up tip design, which consists of a stopper, is developed to straighten the warped die.

Several studies have attempted to minimize the movements when the die is ejected from the sawing tape, die pick up from bond head and die placement, and to the paddle's lead frame. In the semiconductor industry, multiple thin die pick-up methods have been developed to reduce die stress and prevent die crack [5]. Slider peel method is used for die-tape separation. The slider peel method is suitable for the pickup of thin dies [7]. However, this method has the disadvantage of slow output because the direction of the wafer table movement is only at one direction.

An innovation for the ejection system is presented in this paper. The pick-up process will address the handling of die warpage through the pick-up tip collet design. Static pillars together with vacuum and heat for pick up are used to eliminate ejecting movements. In normal practice, the effect of ejecting needle around the contact point only affects limited area; moreover, it can boost local stress greatly by 8 to 10 times, possibly resulting in local damage to chips, as observed by microscope [3]

#### 2 Thin Wafers

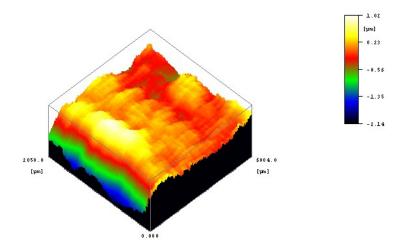

The warpage of thin wafer makes the process more challenging compared with the non-warped wafer. Figure 1 shows the warpage observed on thin wafer.

Fig. 1. Warpage observed on low thickness wafer

The die curvature also intensifies the challenge because of the warpage on thin wafer. High topography on the surface of the die, such as micro bumps, copper pillar, and exposed through silicon via, adds further challenges. Fabricating the holes remains the main challenge for achieving high-performance device structure [17].

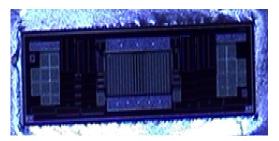

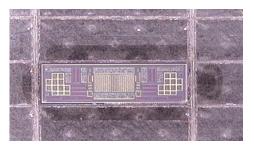

Figure 2 shows an example of the high aspect ratio die with the size of  $32 \times 125$  mils. The challenge of high aspect ratio die is to have a consistent solder coverage with steady placement, including the angular position in the x and y directions. Having low thickness is challenging because the die warpage will be created.

Fig. 2. High aspect ratio die 32 mils x 125 mils

# 3 IC Failures

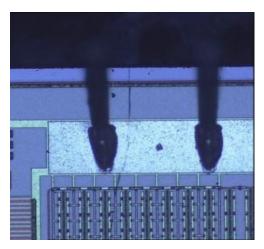

Figure 3 shows the example of a hairline crack. The hairline crack indicates the discontinuation and breakage of circuits in the die, thereby causing the crack and device to malfunction. However, some incidences of marginal hairline crack may occur, and the devices may pass the outgoing test. In some occasions, infrared reflow is performed after post mold cure to expose the marginal hairline crack, and the unfit device is detected at the test later.

Fig. 3. Hairline crack observed

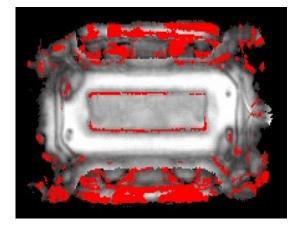

Figure 4 shows the confocal scanning acoustic microscopy (CSAM) result of delamination observed at the edge of the die. However, it does not show the hairline crack across the die. As shown, the top of the die is clean, and the hairline crack is not due to electrical over-stress (EOS) failure.

Fig. 4. CSAM image results

In Figure 5, the mylar imprint mark shows the impact of the ejector pin. Even though the ejector pin has a rounded shape at the tip with certain radius, it can still be harmful for thin dies because they are not strong enough to sustain the impact from the ejector pin.

Fig. 5. Ejector pin imprint on mylar tape

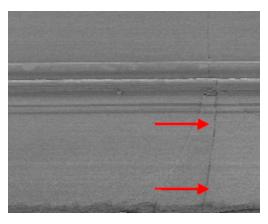

Thus, the process that uses an ejector pin is not suitable for the thin die. Figure 6 shows the hairline crack observed at the side wall of the die. On this basis, the line is not only scratched but also cracked across the die. It shows in the scanning electron microscope (SEM) image of the die's side wall. The red arrows show the crack line. This crack line seems to propagate to several crack lines. On this basis, the device may have critical mechanical stress transmitted to other regions of the die.

Fig. 6. SEM image on side wall of die

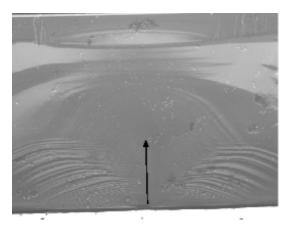

Figure 7 indicates that the crack line is visible from the bottom and propagates to the top. The wavy line formation of the metal compression provides strong evidence that the crack direction starts from the die bottom. The crack location is aligned with the location of the ejector pin. Thus, improvement is required to perform the die pick up process without any issue. Evaluation on the die pick up conditions has been conducted earlier to observe the effect of pick up force and needle size and height on the die crack and needle mark [15].

Fig. 7. SEM image on fractured surface

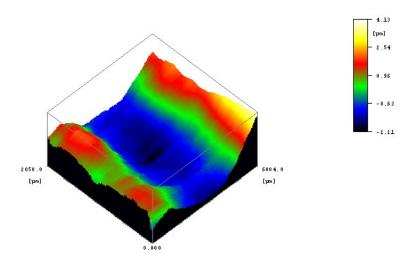

Figures 8 and 9 show the levels of heatsink concavity after die attach and mold processes by using Finite Element Analysis (FEA). The temperature of 380 °C is used for the solder wire melting during the die attach process. A heatsink with high concavity forms. However, when the temperature is approximately 180 °C, the warpage of the mold shows low concavity of the lead frame. The concavity of the die paddle between the die attach and the mold is affected by the relationship of paddle concavity with the environment temperature. The difference applies stress to the die and causes die crack.

However, the warpage of the die paddle has a different level of concavity in other processes.

Fig. 8. High concavity of heatsink after die attach

Fig. 9. Low concavity of heatsink after mold

Moreover, the ejector needle reduces the strength and adds stress to the die. With the addition of other stresses caused by heatsink warpage and mold lock bump, the die easily cracks during or before molding. Local die cracking or scratch marks on the backside are commonly observed in the micro-electronic packaging industry. These marks lead to the failure in subsequent processes or practical services.

#### 4 Methodology

Prior to decapsulation, the outer physical conditions of the unit that is suspected of having the die crack will be checked for any damage, which will be confirmed by nondestructive tests, such as X-ray and CSAM. Basically, the unit will be ruled out to have failure due to external force or EOS failure checking. Investigation is conducted to identify the root cause of the failure through failure analysis and SEM. The complete solution for a crack growth problem includes the determination of the crack path [2]. The hairline crack die is observable from the top of the die. Hence, the crack surface can be inspected further. The die is separated into two pieces, and the crack surface is examined.

Warpage simulation is performed on the die attach process of the soft solder by setting the temperature inside the tunnel between 360 °C and 380 °C. The solder is wetted before the die is placed on top of the die paddle. In such temperature, thermal expansion occurs and causes the paddle to be in warpage. Thus, the thermal expansion coefficient is considered.

The top of the die ejector pepperpot uses a cavity for the die to stop and rest whenever it is aligned for die pick up. The cavity has several pillars that are statically placed at the same level of the surface. Heat is applied to soften the mylar tape. The die and the tape are aligned, and the tape is pulled down and peeled off from the back of the die. The pillar is the only place where the mylar tape is still intact. However, it is a minor force compared with the vacuum from the pick-up tip to lift the die from the mylar tape and place on die paddle. The pillar is heated using the round heater element mounter. The temperature is set at approximately 110 °C to soften the mylar. The time that should be allocated during the pick up to enable the mylar to be pulled down and separated from the bottom of the die is approximately 1 sec. The mounted round heater element is controlled by the temperature thermostat. The heat is set between 100 °C to 120 °C. Normally, it is set at the mid of 110 °C and fine-tuned if any pick up challenge is observed.

When the movement of releasing the die from the mylar tape is completed, the pickup process takes over using the pickup tip. The pickup tip has a special feature of the stopper at the side of the vacuum hole to straighten the warped die before its placement. In this manner, the stability of the die placement can be enhanced without any die tilt issue, and a uniform bond line thickness (BLT) can be achieved. The BLT is important in providing cushioning effect for the die from the package stress. An IC chip device with a high aspect ratio of  $32 \times 125$  mils and a thickness of 75 um, which has a high risk of crack die if using an ejector needle, is used in this study.

The ejectorless system is constructed using ejector cavity with several pillars with zig zag alignment. The zig zag alignment aims to avoid cantilever effect, which may break the die. The vacuum suction holds down the die, and heat is supplied to reduce the adhesion of the sawing tape. Thus, the tape is easily peeled off from the back of the die.

## 5 Results and Discussion

The ejectorless pick up is used to overcome the issue of die cracking for the die attach process. The design of the ejectorless pick up aims to eliminate the usage of the standard ejector pin, which is found unsuitable to be used for thin dies.

Figure 10 shows the top of the ejectorless pepperpot, which supports the die during the pickup process. The contact points to the die are distributed to the pillars, which have large diameter for ejector pin and corner rib support. No movement impact occurs from the bottom of the die because the pillars are static.

Fig. 10.Ejectorless cavity

Figure 11 shows the die on the mylar that is positioned on the ejectorless pepperpot during the die pick up process. The high aspect ratio die is aligned to the cavity. The vacuum is applied subsequently. The heat from the surface of the pillars and corner ribs softens the mylar before the pickup process.

Fig. 11.Die position on ejectorless pepper pot

Figure 12 shows the internal mechanical parts of the ejectorless pepperpot with heater element mounter to heat up the top ejector cavity with temperature of approximately 100 °C to soften the mylar tape before the die pick up process. The assembly is designed in consideration of low change over time between standard and ejectorless pick up.

Fig. 12. Round heater element mounter

Figure 13 shows the side view body of the ejectorless pepperpot. The ejectorless pepperpot has a small top portion, which enables the die pick up process at the side of the wafer from grip ring. The entire die on the wafer must be accessed by the ejectorless pepperpot. Normally, the die pick up process follows the wafer map position, and the ejectorless pepperpot picks up any good die indicated in the wafer map.

Fig. 13.. Ejectorless pepperpot

Figure 14 shows the pickup tip used, which has a design for warp stopper. The warp stopper ensures the die position to be flat during attachment. In this manner, any issue of die attachment material voids that can lead to quality and reliability issue is avoided.

Fig. 14.Pick up tip with warp stopper

The results also show that the device, which has die crack issues whenever it runs in a typical ejector system, has been solved by using the ejectorless pick up system. The system can resolve the crack die issue during the die attach process or weaken die strength and failure during subsequent processes. The improvement shows that the cracking issue is improved to zero incidence. Table 1 shows the crack issue detected after decapsulation on the electrical test failure on five production lots. Table 2 indicates

the result of 100% yield of electrical test after temperature cycle test, TC500. No crack die is observed after decapsulation on three qualification lots.

|   | DC Yield (%) | Decap Results (crack die) |

|---|--------------|---------------------------|

| 1 | 96.88        | 4/5                       |

| 2 | 95.77        | 5/5                       |

| 3 | 91.27        | 5/5                       |

| 4 | 94.50        | 3/5                       |

| 5 | 81.30        | 5/5                       |

Table 1. Test and decap results before optimization

**Table 2.** Optimization qual test result after TC500

| Qual#  | In | Out | Yield (%) | Decap Results (crack die) |

|--------|----|-----|-----------|---------------------------|

| Qual 1 | 50 | 50  | 100       | 0/5                       |

| Qual 2 | 50 | 50  | 100       | 0/5                       |

| Qual 3 | 50 | 50  | 100       | 0/5                       |

#### 6 Conclusion

The proposed method offers a long-awaited solution of the die pick up method for ultra-thin die, which is required for solving die cracking issue. However, the process takes a long time. As a result, the normal ejector pin usage may lead to slow output (units per hour). The shortcomings are not a major problem because the solutions for the cracking of ultra-thin dies with high aspect ratio die are more essential than the shortcomings.

### 7 References

- [1] Zakaria Abdullah, Letcheemana Vigneswaran, Amy Ang & Goh Zhi Yuan. (2012). Die attach capability on ultra-thin wafer thickness for power semiconductor. 35th IEEE/CPMT International Electronics Manufacturing Technology Conference (IEMT): 1 – 5. <u>https://doi.org/10.1109/iemt.2012.6521812</u>

- [2] F. Arabi, L. Theolier, T. Youssef, M. Medina, J.-Y. Deletage & E. Woirgard. (2017). Effect of voids on crack propagation in AuSn die attach for high-temperature power modules. 18th International Conference on Thermal, Mechanical and Multi-Physics Simulation and Experiments in Microelectronics and Microsystems (EuroSimE):1-6. <u>https://doi.org/10. 1109/eurosime.2017.7926230</u>

- [3] Bo Peng, YongAn Huang, ZhouPing Yin & YouLun Xiong. (2011). On the analysis of dynamic effect in the die pick-up process. 12th International Conference on Electronic Packaging Technology and High-Density Packaging: 1 – 4. <u>https://doi.org/10.1109/ icept.2011.6066916</u>

- [4] Eun-Beom Jeon, Sung-Hyeon Park, Yun-Sik Yoo & Hak-Sung Kim. (2016). Analysis of Interfacial Peeling of an Ultrathin Silicon Wafer Chip in a Pick-Up Process Using an Air Blowing Method. IEEE Transactions on Components, Packaging and Manufacturing Technology: 1696 – 1702. <u>https://doi.org/10.1109/tcpmt.2016.2612238</u>

- [5] Richard Qian & Yong Liu. (2016). Thin and large die assembly pick up process optimization by dynamic modeling. 17th International Conference on Electronic Packaging Technology (ICEPT): 147 – 152. <u>https://doi.org/10.1109/icept.2016.7583108</u>

- [6] Huiqiang Shen, Lezhi Ye, Liang Tang & Ziyang Liu. (2015). Study on thin die pick-up process based on Taguchi method. 16th International Conference on Electronic Packaging Technology (ICEPT): 1344 – 1347. <u>https://doi.org/10.1109/icept.2015.7236827</u>

- [7] Chuichi Miyazaki, Haruo Shimamoto, Toshihide Uematsu, Yoshiyuki Abe, Kosuke Kitaichi , Tadahiro Morifuji & Shoji Yasunaga. (2010). Development of high accuracy wafer thinning and pickup technology for thin wafer(die). IEEE CPMT Symposium Japan: 1 – 4. <u>https://doi.org/10.1109/cpmtsympj.2010.5679528</u>

- [8] Wai Shan Liau & Tek Keong Gan. (2018). 'Collet Auto Clean System', A Smart Automatic Solution for Die Bonding Pick Up Tool Lifespan & Throughput Enhancement. IEEE 38th International Electronics Manufacturing Technology Conference (IEMT): 1- 6. <u>https://doi.org/10.1109/iemt.2018.8511724</u>

- [9] J. Medding, R. Stalder, M. Niederhauser & P. Stoessel. (2004). Thin die bonding techniques. IEEE/CPMT/SEMI 29th International Electronics Manufacturing Technology Symposium: 68 – 73. <u>https://doi.org/10.1109/iemt.2004.1321634</u>

- [10] Carine Gerets, Jaber Derakhshandeh, Teng Wang, Giovanni Capuz, Arnita Podpod, Caroline Demeurisse, Kenneth June Rebibis, Andy Miller, Gerald Beyer & Eric Beyne. (2014). Picking large thinned dies with high topography on both sides. IEEE 16th Electronics Packaging Technology Conference (EPTC): 175 179. <u>https://doi.org/10.1109/eptc.2014.7028289</u>

- [11] Y. Sing Chan, Julie Chew, Chu Hua Goh, Siang Kuan Chua & Alfred Yeo. (2014). Characterization of dicing tape adhesion for ultra-thin die pick-up process. IEEE 16th Electronics Packaging Technology Conference (EPTC): 554 – 557. <u>https://doi.org/10.1109/ eptc.2014.7028390</u>

- [12] Wei Sun, W.H. Zhu, F.X. Che, C.K. Wang, Anthony Y.S. Sun & H.B. Tan. (2007). Ultrathin Die Characterization for Stack-die Packaging. Proceedings 57th Electronic Components and Technology Conference: 1390 – 1396. <u>https://doi.org/10.1109/ectc.2007.</u> <u>373976</u>

- [13] Ibrahim Ahmad, Nur Nadia Bachok, Ng Cheong Chiang, Meor Zainal Meor Talib, Mohamad Firdaus Rosle, Farah Liyana Ab Latip, Zurlinda Asma Aziz. (2007). Evaluation of Different Die Attach Film and Epoxy Pastes for Stacked Die QFN Package. 9th Electronics Packaging Technology Conference (EPTC):869 – 873. <u>https://doi.org/10.1109/ eptc.2007.4469691</u>

- [14] Izhan Abdullah, Ng Cheong Chiang, Umizaimah Mokhtar, Asmawatie Said, Meor Zainal Meor Talib, Ibrahim Ahmad. (2007). Warpage and Wire Sweep Analysis of QFN Molded Strip using Experimental and Modeling Methods. 9th Electronics Packaging Technology Conference, EPTC:494 – 498. <u>https://doi.org/10.1109/eptc.2007.4469692</u>

- [15] A. Jalar, M. F. Rosle, M. A. A. Hamid. (2008). Die Attach Film Performance in 3D QFN Stacked Die. WSEAS Transactions on Applied and Theoretical Mechanics: Vol. 3, Issue 3: 104-113.

- [16] A. R. A. Rahman, Nazrul Anuar Nayan. (2019). Critical challenges and solutions for device miniaturization in integrated circuit packaging technology. Journal of Engineering and Applied Sciences: Vol. 13, Issue 15: 6025-6032.

- [17] Nur Dalila Mohd Zamani, Ahmad Rifqi Md Zain, Burhanuddin Yeop Majlis. 2016. Modelling of 2-D Gallium Nitride (GaN) Photonic Crystal. (2016). 12th IEEE International Conference on Semiconductor Electronics (ICSE 2016): 54-56. <u>https://doi.org/10. 1109/smelec.2016.7573589</u>

- [18] Liqun Hou, Shudong Tan,Lei Yang, Zhijuan Zhang, Neil W. Bergmann. (2017). Autonomous Wireless Sensor Node with Thermal Energy Harvesting for Temperature Monitoring of Industrial Devices. International Journal of Online and Biomedical Engineering (iJOE): Vol. 13 No. 4. <u>https://doi.org/10.3991/ijoe.v13i04.6802</u>

- [19] Xue-Wen Yu. (2017). Design and Application of Wireless Sensor Network Monitoring Software Based on LABVIEW. International Journal of Online and Biomedical Engineering (iJOE): Vol. 13 No. 5. <u>https://doi.org/10.3991/ijoe.v13i05.7047</u>

- [20] Khoo Voon Ching. (2019). A Case Study of Return on Investment for Multi-sites Test Handler in The Semiconductor Industry Through Theory of Industry 4.0 ROI Relativity. International Journal of Online and Biomedical Engineering (iJOE): Vol. 7 No. 3. <u>https://doi.org/10.3991/ijes.v7i3.11057</u>

#### 8 Authors

Ahmad R. A. Rahman is a postgraduate student and currently pursuing his Ph.D in Faculty of Engineering & Built Environment, Universiti Kebangsaan Malaysia (UKM). He is having several years of semiconductor manufacturing experience. Email: p94324@siswa.ukm.edu.my

**Ir. Dr. Nazrul Anuar Nayan** is a professional engineer and a senior lecturer at the Faculty of Engineering & Built Environment, Universiti Kebangsaan Malaysia (UKM). He had several years of semiconductor industry experience.

Email: <u>nazrul@ukm.edu.my</u>

Article submitted 2020-04-09. Resubmitted 2020-04-26. Final acceptance 2020-04-26. Final version published as submitted by the authors.